VREDUCEPH - REDUCE Packed Half

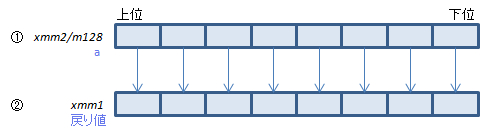

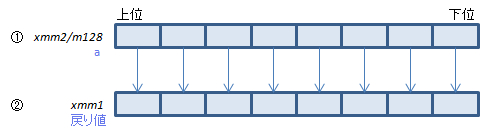

VREDUCEPH xmm1{k1}{z}, xmm2/m128/m16bcst, imm8 (V5+FP16+VL

__m128h _mm_reduce_ph(__m128h a, int imm8)

__m128h _mm_mask_reduce_ph(__m128h s, __mmask8 k, __m128h a, int imm8)

__m128h _mm_maskz_reduce_ph(__mmask8 k, __m128h a, int imm8)

imm8の指定に従って①の小数点以下nビットを残してその下を丸めた実数を作り

①からそれを引いた差を②にセットする

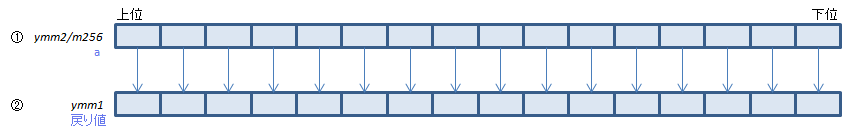

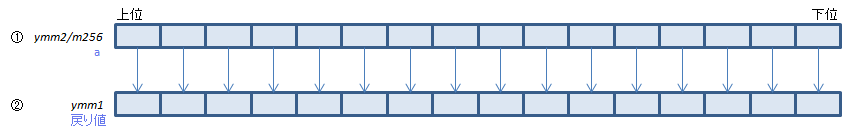

VREDUCEPH ymm1{k1}{z}, ymm2/m256/m16bcst, imm8 (V5+FP16+VL

__m256h _mm256_reduce_ph(__m256h a, int imm8)

__m256h _mm256_mask_reduce_ph(__m256h s, __mmask16 k, __m256h a, int imm8)

__m256h _mm256_maskz_reduce_ph(__mmask16 k, __m256h a, int imm8)

imm8の指定に従って①の小数点以下nビットを残してその下を丸めた実数を作り

①からそれを引いた差を②にセットする

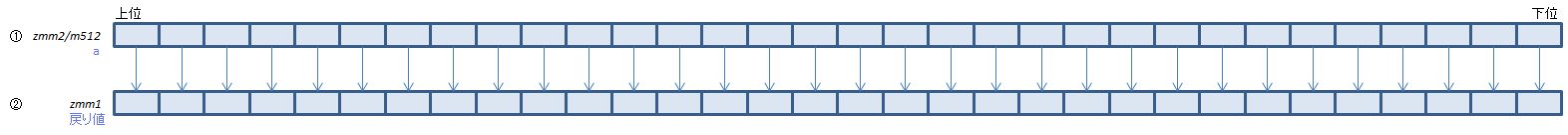

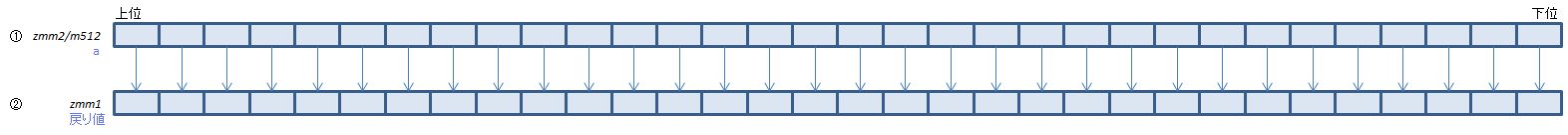

VREDUCEPH zmm1{k1}{z}, zmm2/m512/m16bcst{sae}, imm8 (V5+FP16

__m512h _mm512_reduce_ph(__m512h a, int imm8)

__m512h _mm512_mask_reduce_ph(__m512h s, __mmask32 k, __m512h a, int imm8)

__m512h _mm512_maskz_reduce_ph(__mmask32 k, __m512h a, int imm8)

__m512h _mm512_reduce_round_ph(__m512h a, int imm8, int sae)

__m512h _mm512_mask_reduce_round_ph(__m512h s, __mmask32 k, __m512h a, int imm8, int sae)

__m512h _mm512_maskz_reduce_round_ph(__mmask32 k, __m512h a, int imm8, int sae)

imm8の指定に従って①の小数点以下nビットを残してその下を丸めた実数を作り

①からそれを引いた差を②にセットする

imm8の指定方法

| bit |

指定するもの |

| 7:4 |

小数点以下に残すビット数を0~15で指定

0を指定すると小数点以下が0の実数にする(ROUNDPD/ROUNDPSと同様の動作)

|

| 3 |

0=precision例外マスクはMXCSRに従う

1=MXCSRの設定にかかわらずprecision例外をマスクする

|

| 2 |

0=丸め方法をビット1:0で指定する

1=丸め方法はMXCSRの設定に従う

|

| 1:0 |

00=近い方向に丸める 等距離のときは残すビットの最下位が0になる方向に丸める

01=マイナス無限大方向に丸める

10=プラス無限大方向に丸める

11=ゼロ方向に丸める

|

x86/x64 SIMD命令一覧表

フィードバック