VPSRAVD - Packed Shift Right Arithmetic Variable Dword

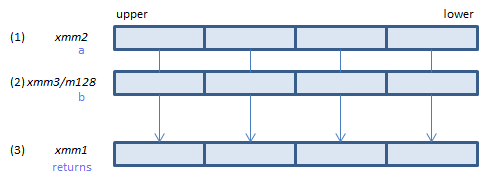

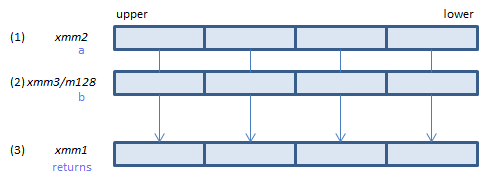

VPSRAVD xmm1, xmm2, xmm3/m128 (V2

__m128i _mm_srav_epi32(__m128i a, __m128i b)

VPSRAVD xmm1{k1}{z}, xmm2, xmm3/m128/m32bcst (V5+VL

__m128i _mm_mask_srav_epi32(__m128i s, __mmask8 k, __m128i a, __m128i b)

__m128i _mm_maskz_srav_epi32(__mmask8 k, __m128i a, __m128i b)

For each DWORD, set (1) >> (2) to (3). Emptied upper bits are filled with the initial sign bit.

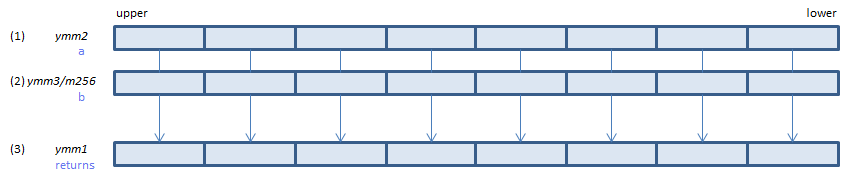

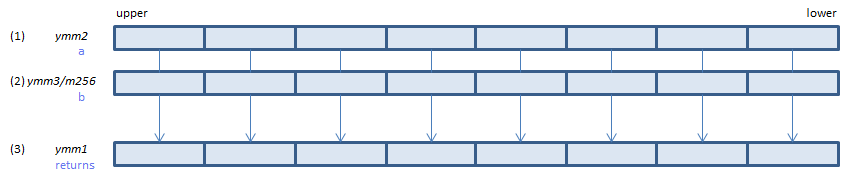

VPSRAVD ymm1, ymm2, ymm3/m256 (V2

__m256i _mm256_srav_epi32(__m256i a, __m256i b)

VPSRAVD ymm1{k1}{z}, ymm2, ymm3/m256/m32bcst (V5+VL

__m256i _mm256_mask_srav_epi32(__m256i s, __mmask8 k, __m256i a, __m256i b)

__m256i _mm256_maskz_srav_epi32(__mmask8 k, __m256i a, __m256i b)

For each DWORD, set (1) >> (2) to (3). Emptied upper bits are filled with the initial sign bit.

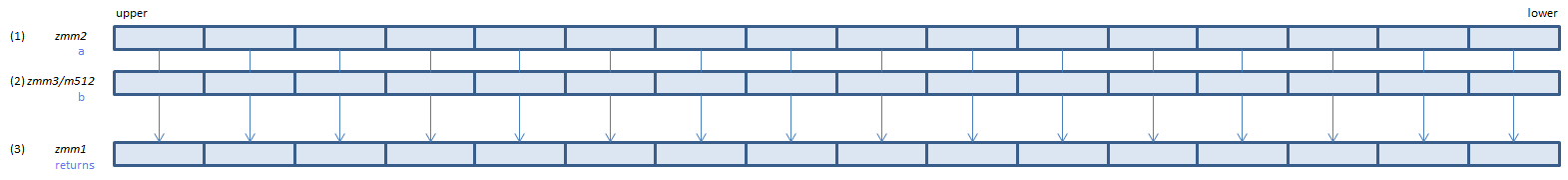

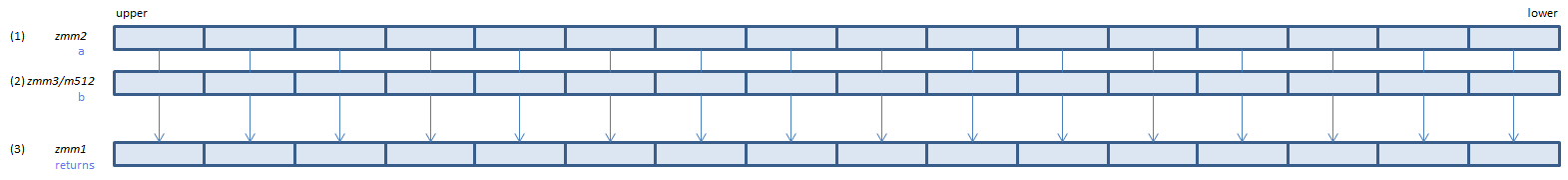

VPSRAVD zmm1{k1}{z}, zmm2, zmm3/m512/m32bcst (V5

__m512i _mm512_srav_epi32(__m512i a, __m512i b)

__m512i _mm512_mask_srav_epi32(__m512i s, __mmask16 k, __m512i a, __m512i b)

__m512i _mm512_maskz_srav_epi32(__mmask16 k, __m512i a, __m512i b)

For each DWORD, set (1) >> (2) to (3). Emptied upper bits are filled with the initial sign bit.

x86/x64 SIMD Instruction List

Feedback