VMOVDQA32 - MOVe DoubleQword Aligned 32

VMOVDQU32 - MOVe DoubleQword Unaligned 32

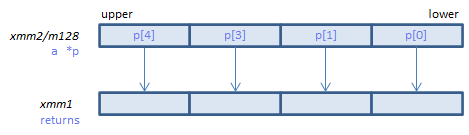

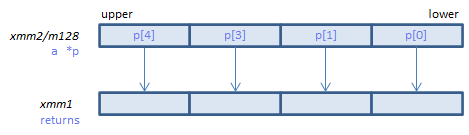

VMOVDQA32 xmm1{k1}{z}, xmm2/m128 (V5+VL 16-byte alignment required. also for void*

__m128i _mm_mask_load_epi32(__m128i s, __mmask8 k, void* p)

__m128i _mm_maskz_load_epi32(__mmask8 k, void* p)

__m128i _mm_mask_mov_epi32(__m128i s, __mmask8 k, __m128i a)

__m128i _mm_maskz_mov_epi32(__mmask8 k, __m128i a)

VMOVDQU32 xmm1{k1}{z}, xmm2/m128 (V5+VL no alignment required.

__m128i _mm_mask_loadu_epi32(__m128i s, __mmask8 k, void* p)

__m128i _mm_maskz_loadu_epi32(__mmask8 k, void* p)

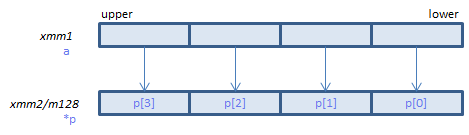

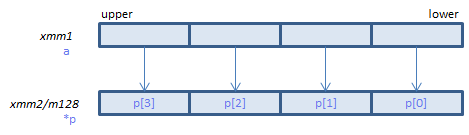

VMOVDQA32 xmm2/m128{k1}{z}, xmm1 (V5+VL 16-byte alignment required. also for void*

void _mm_mask_store_epi32(void* p, __mmask8 k, __m128i a)

VMOVDQU32 xmm2/m128{k1}{z}, xmm1 (V5+VL no alignment required.

void _mm_mask_storeu_epi32(void* p, __mmask8 k, __m128i a)

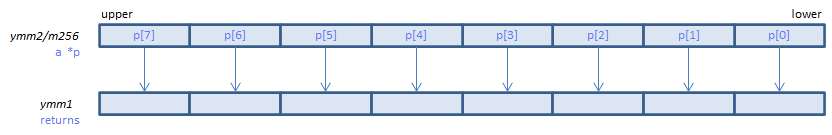

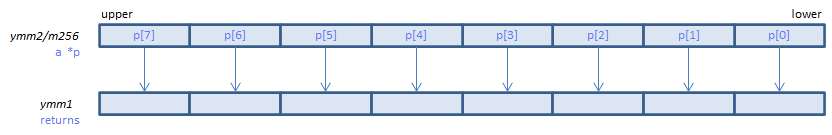

VMOVDQA32 ymm1{k1}{z}, ymm2/m256 (V5+VL 32-byte alignment required. also for void*

__m256i _mm256_mask_load_epi32(__m256i s, __mmask8 k, void* p)

__m256i _mm256_maskz_load_epi32(__mmask8 k, void* p)

__m256i _mm256_mask_mov_epi32(__m256i s, __mmask8 k, __m256i a)

__m256i _mm256_maskz_mov_epi32(__mmask8 k, __m256i a)

VMOVDQU32 ymm1{k1}{z}, ymm2/m256 (V5+VL no alignment required.

__m256i _mm256_mask_loadu_epi32(__m256i s, __mmask8 k, void* p)

__m256i _mm256_maskz_loadu_epi32(__mmask8 k, void* p)

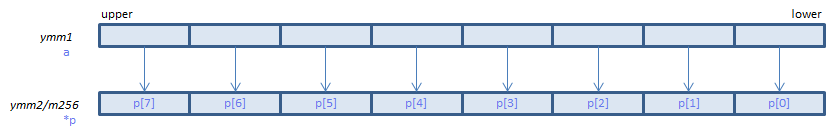

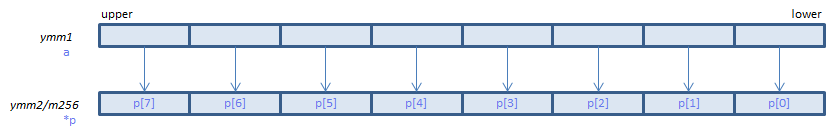

VMOVDQA32 ymm2/m256{k1}{z}, ymm1 (V5+VL 32-byte alignment required. also for void*

void _mm256_mask_store_epi32(void* p, __mmask8 k, __m256i a)

VMOVDQU32 ymm2/m256{k1}{z}, ymm1 (V5+VL no alignment required.

void _mm256_mask_storeu_epi32(void* p, __mmask8 k, __m256i a)

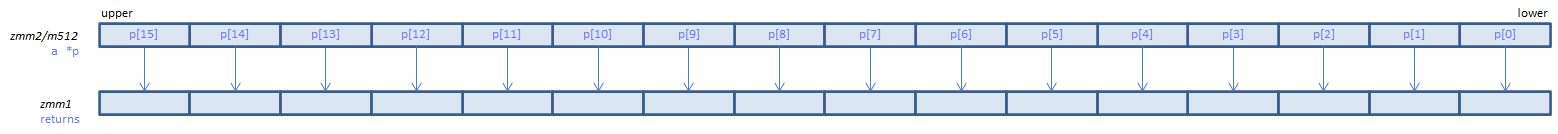

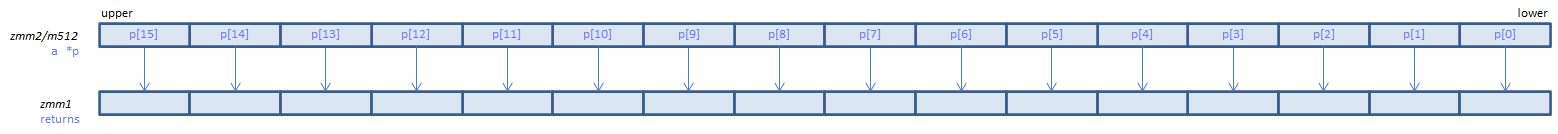

VMOVDQA32 zmm1{k1}{z}, zmm2/m512 (V5 64-byte alignment required. also for void*

__m512i _mm512_load_si512(__m512i s, void* p)

__m512i _mm512_mask_load_epi32(__m512i s, __mmask16 k, void* p)

__m512i _mm512_maskz_load_epi32(__mmask16 k, void* p)

__m512i _mm512_mask_mov_epi32(__m512i s, __mmask16 k, __m512i a)

__m512i _mm512_maskz_mov_epi32(__mmask16 k, __m512i a)

VMOVDQU32 zmm1{k1}{z}, zmm2/m512 (V5 no alignment required.

__m512i _mm512_loadu_si512(__m512i s, void* p)

__m512i _mm512_mask_loadu_epi32(__m512i s, __mmask16 k, void* p)

__m512i _mm512_maskz_loadu_epi32(__mmask16 k, void* p)

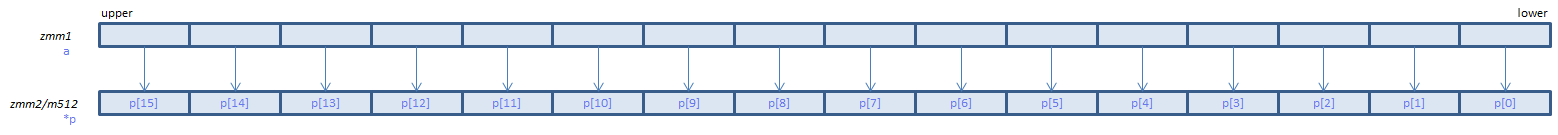

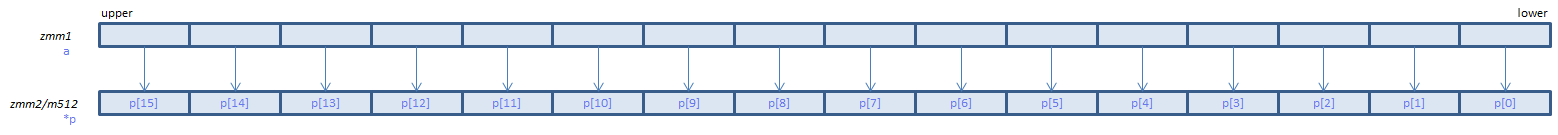

VMOVDQA32 zmm2/m512{k1}{z}, zmm1 (V5 64-byte alignment required. also for void*

void _mm512_store_si512(void* p, __m512i a)

void _mm512_mask_store_epi32(void* p, __mmask16 k, __m512i a)

VMOVDQU32 zmm2/m512{k1}{z}, zmm1 (V5 no alignment required.

void _mm512_storeu_si512(void* p, __m512i a)

void _mm512_mask_storeu_epi32(void* p, __mmask16 k, __m512i a)

x86/x64 SIMD Instruction List

Feedback